(三)多体模块系统

1. 背景

- CPU(10ms 量级)和内存(200ms 量级)速度不匹配,内存成为限制 CPU 利用率的瓶颈;

- 解决方案

- 双口 RAM;

- 多体模块系统

- 单体多字;

- 多体并行;

- 高位顺序方式;

- 低位交叉方式;

- 高速 cache;

2. 双口 RAM

- 概念:一种高速存储器,具有两组相互独立的读写控制线路,可以同时进行读写;

- 冲突问题

- 当两端口地址不相同时,在两端口上进行读写操作,不会发生冲突;

- 当**两个端口同时存取同一存储单元(地址码)**时,便发生冲突。此时,由判断逻辑来决定哪一个端口进行读写操作;

⭐3. 多体模块系统

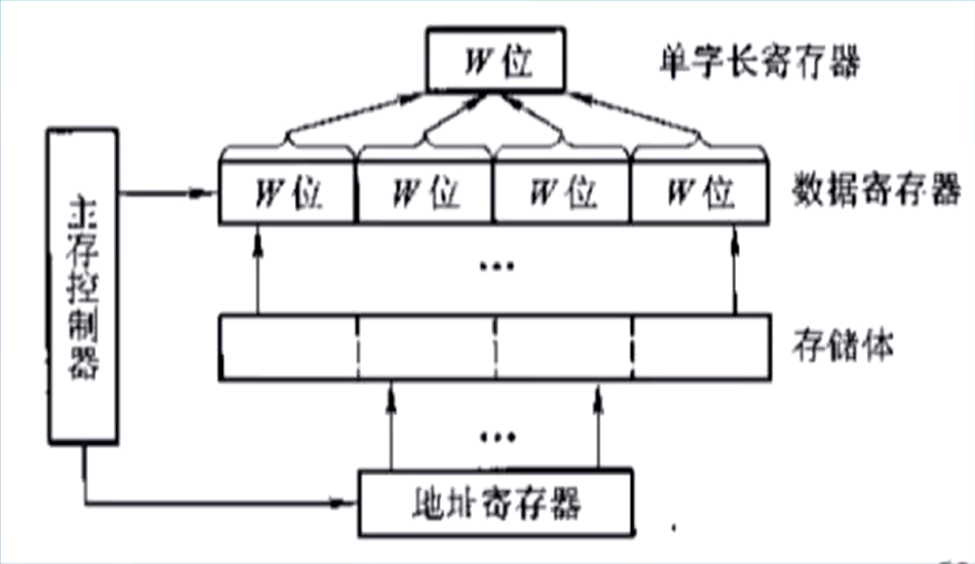

3.1. 单体多字

- 概念:在一个存取周期内,从同一地址取出多条指令,然后再逐条将指令送至 CPU 执行;

- 适用情况:程序和数据在内存中连续存放,且大小已知;

- 优点:增大了存储器带宽,提高了单体存储器的速度;

- 实例分析:取 4 条连续存放的指令/数据;

- 单体单字:需要给出 4 次地址,消耗 8 存取周期;

- 单体多字:给出 1 次首地址,存储器连续返回 4 个数据,共 5 个存取周期;

3.2. 多体并行

概念:主存储器分为多个独立的模块。

- 每个模块有相同的容量和存取速度;

- 每个模块有独立的 MAR, MDR,地址译码,驱动和读写电路;

- 模块之间能并行工作,也可以交叉工作;

- 并行存取的数据都经过同一条数据总线,因此需要分时传送;

一个由若干模块组成的存储器是线性编址,这些地址在模块中有两种安排方式:(1) 顺序,(2) 交叉;

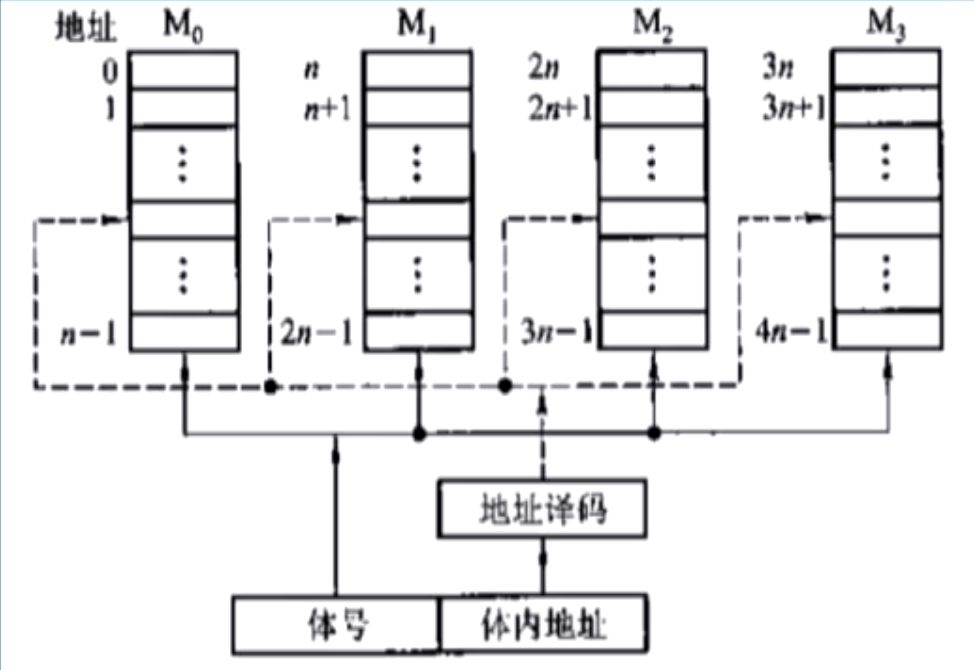

高位顺序方式

- 数据在每个模块

内按顺序存放,每个模块的体内地址是连续的; - 地址的高位表示体号(模块号),低位表示体内地址;

- 并发原理:不同的请求源在同一时刻可访问不同的模块;

- 不同的请求源:指的是程序存放在不同模块中的请求源;

- 优点

- 利用了局部性的特点(程序较短时间内更容易访问连续的数据);

- 扩展性好;

- 缺点:对于单一请求源,一般不能起到加速作用(单一请求源访问一般局限在一个模块中);

- 数据在每个模块

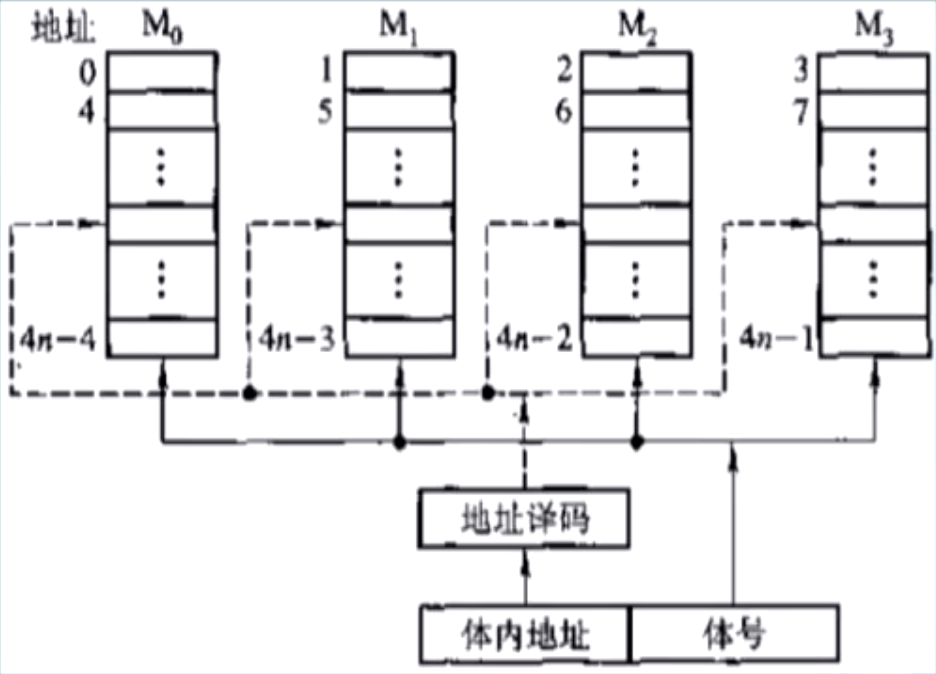

低位交叉方式

- 原来相邻的地址被分到相邻模块中进行存储;

- 程序连续存放在相邻的模块中;

- 地址的高位表示体内地址,低位表示体号;

- 体号 = 内存编号 mod 体数(模块个数);

- 并发原理:同一请求源在同一时刻可访问不同的模块;

- 优点:单一请求源加速;

- 缺点

- 丧失局部性;

- 扩展性差(增加模块后所有数据要重排);

- 冲突访问

- 考研中一般认为,存取周期

和数据总线的传输周期 满足 ; - 若相邻访问落在同一个模块,则第二个访问到达时,模块尚未完成一个周期,无法处理请求;

- 考研中一般认为,存取周期

- 实例分析:顺序访问和低位交叉方式的存取耗时(设传输周期

,存取周期 ,存取 个单元) - 顺序访问:

; - 1)CPU 将第一个地址发送给存储器,耗时

,送到后存储器开始读/写; - 2)存储器读写第一个地址时,MAR 可以暂存下一个地址,因此 CPU 马上发送第二个地址;

- 3)存储器需要完成一个

后才能处理第二个地址,因此 CPU 需要等到 时刻才能发送第三个地址; - 4)每次存储器读/写完后,需要用

时间将数据回传 CPU; - 5)以此类推,共需要

时间处理完所有请求,还需要 时间回传最后一个数据,总耗时 ;

- 1)CPU 将第一个地址发送给存储器,耗时

- 低位交叉方式:

, - 假设:(1)

个地址分别存储在 个不同模块上,(2) 和 恰好满足 ; - 1)CPU 将第一个地址发送给模块 1,耗时

,送到后模块 1 开始读/写; - 2)流水线:模块 1 工作时,CPU 继续将第二个地址发送给模块 2,以此类推;

- 3)第

个模块在 时刻收到请求,并立即开始处理,最后一个模块处理完的时刻为 ; - 4)再加上回传时间,即

; - 5)注意:这里恰好回传和正传没有冲突,若

过大,则要考虑总线分时问题, 可能要更大;

- 假设:(1)

- 顺序访问:

习题

- 四体低位交叉存储器,存取周期

;每个单体存储容量 1M×32 位,则下列说法正确的是

A. 在 100ns 内,存储器可向 CPU 提供 128 位数据;

B. 在 400ns 内,存储器可向 CPU 提供 128 位数据;

C. 存储器容量 4MB;

D. 存储器容量 16MB;

答案:B, D

解析:一般考研题目默认

, 是体数(模块数),所以可得 ; - A. 100ns 为总线传输周期,最多 32 位,错;

- B. 流水线全模块运行时,从第一个模块完成存取开始,四个模块连续完成存取,连续向总线提供 32 位数据,故 400ns 内可以提供 32×4 = 128 位,对;

- 此时流水线称为满载流水线;

- C, D. 存储容量 1M×4B×4=16MB;

- 四体低位交叉存储器,存取周期

- 四体交叉编址,总线上有如下的连续地址访问:0x8005,0x8006,0x8007,0x8008,0x8001,0x8002,0x8003,0x8004,0x8000,则可能发生冲突的地址对为

- A. 0x8004 和 0x8008;

- B. 0x8002 和 0x8007;

- C. 0x8001 和 0x8008;

- D.0x8000 和 0x8004;

- 答案:D

- 解析:取模算体号即可。D 选项都是访问 0 号模块,因此会冲突;

- 拓展 1:冲突时,先来的地址先响应,后来的地址需要等待存储器完成一个周期才能被处理;

- 拓展 2:因为默认

,所以两个同体的地址间隔 个地址就可以不发生冲突;

- 四体结构,每个模块字长 32 位,存取周期 200ns,设数据总线宽度 32 位,传输周期 50ns,求顺序存储和交叉存储的带宽;

- 答案:顺序存储 160Mbps,交叉存储 370Mbps;

- 解析:因为

,故考虑连续读取 4 个字所花时间(此时交叉编址流水线满载,吞吐量最大); - 存储器带宽定义:存储器单位时间内读/写的数据量,注意此处不考虑前后的总线时间;

- 顺序:

,带宽 ; - 交叉:从第一个模块开始工作,到最后一个模块结束处理,则

,带宽 ;