(二)总线的通信控制

1. 概念

1.1. 主从设备

- 主设备:获得总线控制权,发起数据传输的设备;

- 从设备:被主设备寻址,被动进行数据传输的设备;

- 例:CPU 对内存访存,CPU 主设备,内存从设备;

1.2. 总线周期

- 概念:通常将完成一次总线操作的时间称为总线周期;

- 总线周期的阶段:大致分为 4 个

- 申请分配:主设备/模块申请,总线仲裁决定/分配;

- 总线仲裁:多个设备同时提出请求时,需要总线控制器决定哪些设备优先使用总线;

- 是由总线分时的特性导致的;

- 寻址:主设备向从设备给出地址和命令;

- 传数阶段:主从设备通过总线交换数据;

- 结束阶段:主设备释放总线控制权;

- 申请分配:主设备/模块申请,总线仲裁决定/分配;

2. 总线通信方式

2.1. 同步定时

- 概念:采用一个统一的时钟信号协调发送和接收双方的传输关系;

- 时钟信号产生的时间间隔相等;

- 若干个将间隔构成一个总线周期;

- 各模块在不同阶段的操作都统一规定(如:给地址—给命令—传输数据—撤销请求);

- 特点

- 传输频率较高;

- 当各设备存取时间差距大时,会降低设备的利用效率;

- 适用:总线长度较短、各模块存取速度接近的系统;

2.2. 异步定时

概念:不采用同步时钟信号,而是采用主从设备之间的握手信号来同步;

主设备负责发送 "请求" 信号,从设备发送 "回答" 信号;

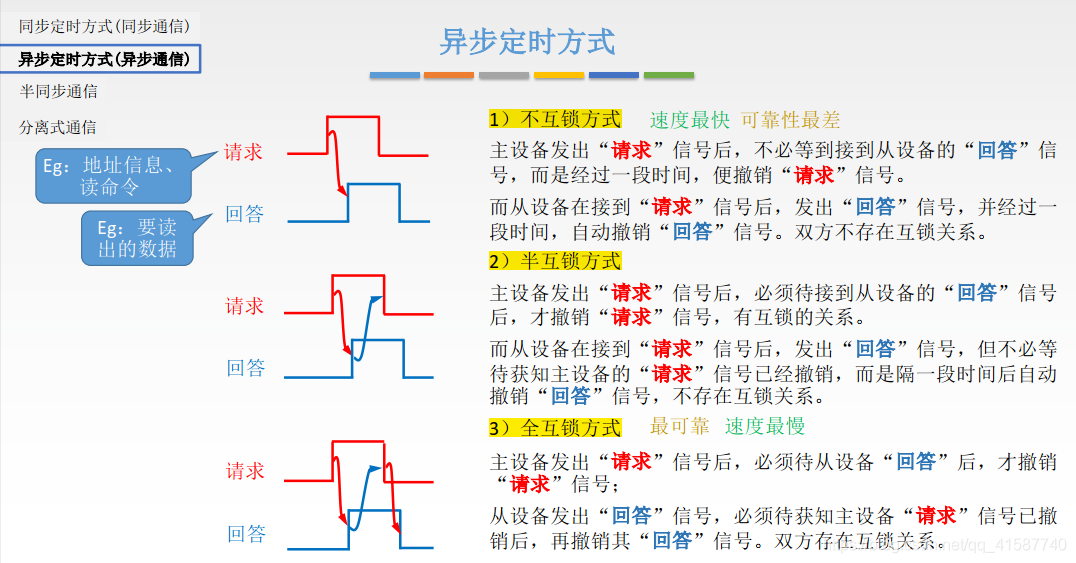

异步定时的三种实现方式

方式 主设备发送请求后 从设备发送回答后 不互锁 不等待回答,过一段时间自动撤销请求 不等待请求撤销,过一段时间自动撤销回答 半互锁 必须等待回答才能撤销请求 不等待请求撤销,过一段时间自动撤销回答 全互锁 必须等待回答才能撤销请求 必须等待请求撤销才能撤销回答 图示

特点

- 速度:不互锁 > 半互锁 > 全互锁;

- 可靠性:全互锁 > 半互锁 > 不互锁

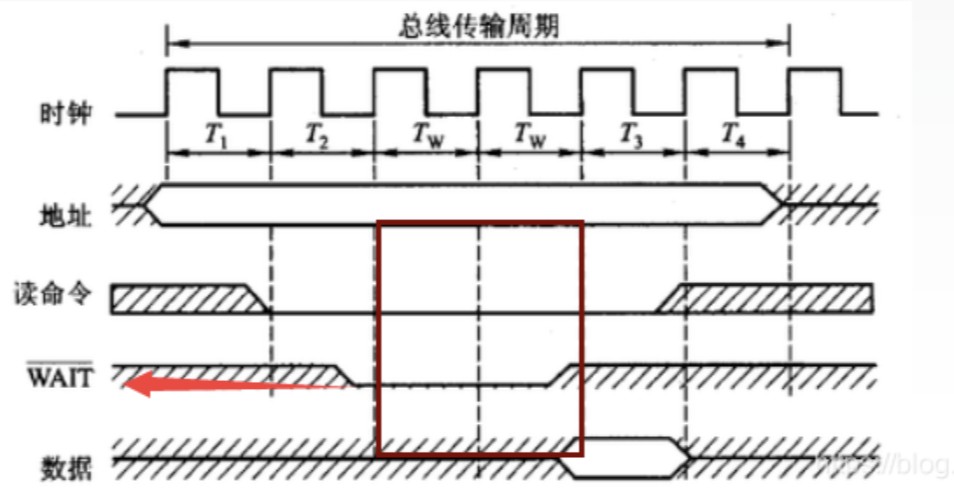

2.3. 半同步

概念:同步 + 异步;

- 同步:发送和接收双方仍采用一个系统时钟来同步;

- 异步:增加一条等待响应信号

,允许存取速度不同的模块通信;

图示

2.4. 分离式

- 概念:采用同步方式,但将总线使用权细分到一个总线周期为单位,而不是一个操作;

- 主设备申请占用总线,向从设备传输命令和参数,传输完成后释放控制权;

- 从设备在数据准备完成前不占用总线;

- 从设备数据准备完毕后,申请占用总线,向主设备回传数据;

- 即此时双方身份互换;

- 特点

- 主从设备均可申请占用总线;

- 仍采用系统时钟同步;

- 显著提高总线利用率;

习题

- 单周期处理器中,指令周期和 CPU 时钟周期相等,则下列说法错误的是

- A. 可采用和单总线结构数据通路;

- B. 处理器时钟频率较低;

- C. 指令执行过程中,控制信号不变;

- D. 每条指令 CPI 为 1;

- 答案:A

- 解析

- A. 因为指令执行需要取指,同时指令的行为可能会向存储单元写回数据。单总线在一个时钟周期内不可能完成,故 A 错;

- B. 因为指令执行需要考虑到存储器的速度,此题中指令执行频率和 CPU 相同了,故 CPU 频率只能降低到其相同水平;

- C. 一个时钟周期内控制信号不能改变,故 C 对;

- D. 对;

- 异步串行传输系统中,每秒传输 120 帧,每帧包含 1 起始位,7 数据位,1 奇偶校验位,1 终止位,计算波特率和比特率;

- 答案:波特率 1200bps,比特率 840bps;

- 解析:区分波特率和比特率

- 波特率:每秒传输的码元数量,本题中码元为 0/1,即二进制位数;

- 比特率:每秒传输的有效数据位数;

- 每帧包含 10 码元,7 有效数据,每秒 120 帧,故得出 1200bps 波特率,840bps 比特率;